Cadence 16.5埋阻埋容PCB设计

------樊渝江

这是我写的第1次Cadence笔记,写的不是很好希望大家纠正。

之前1直使用的是Cadence 15.7,这次由于要使用埋阻埋容工艺所有更改成了16.5,16.5给我的感觉是很多工具都变位置了,还是摸索了1下才找到的,但封装和原理图的制作界面没怎样变还是保存之前界面。

开始我们的埋阻埋容设计了。

1.原理图网表输出。

为了方便我就不细说原理图是怎样建立的了,和15.71样的没甚么区分。

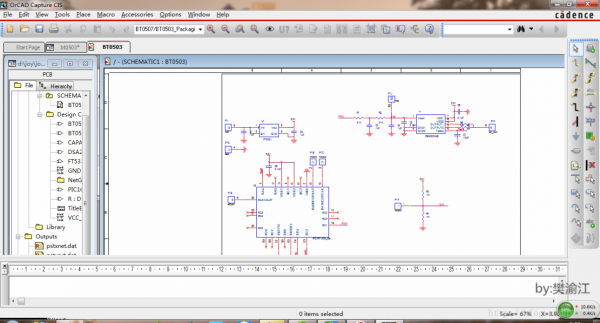

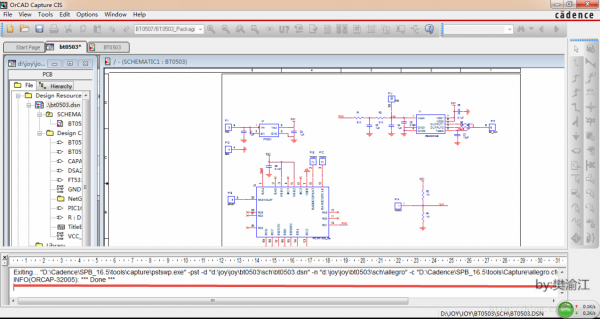

上图就是我建好的原理图,在导出网表之前我们要把每一个期间的封装添上,然落后行DRC检查要不然在导网表的时候会报错。(我已把封装添加进去了)

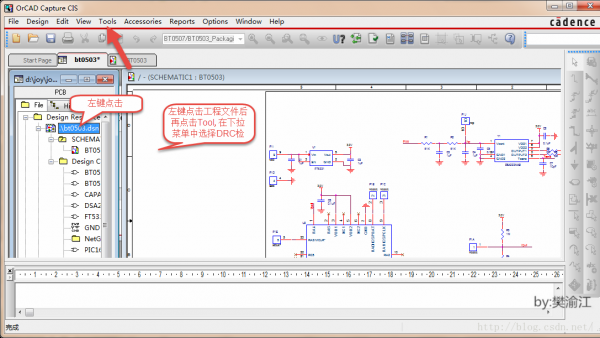

先运行DRC检查,左键点击工程文件,等菜单栏变化后,点击Tools – Design Rules Check..

然后会弹出出以下对话框

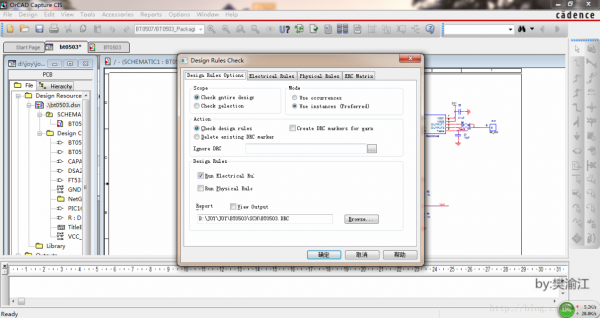

这个对话框就是DRC校验的设置对话框,如果没的特殊要的话,直接默许设置就OK了(15.7需要自己选,16.5默许的已完全足够了)。

软件就开始直接检查,有毛病就会弹1个对话框出来告知你问题在哪,没有错就会直接通过。

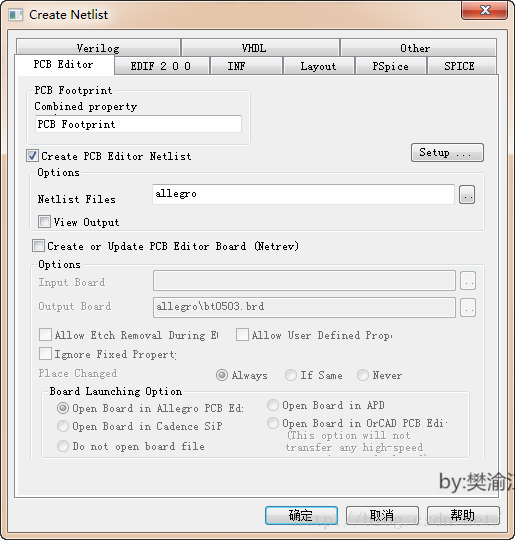

DRC检查过后下1步就开始导出网表,点击Tools –Create Netlist,就会出现以下对话框。

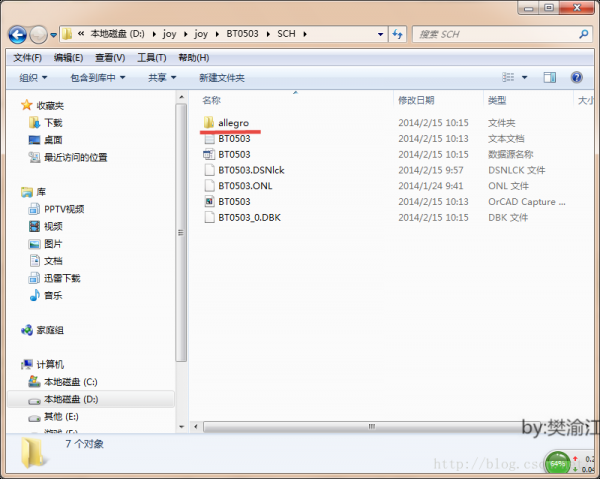

第1次导出网表就把Create PCB Editor Netlist 那栏打上勾,网表输出的路径就是在你原理图工程下,成功后会多1个allegro的文件夹,里面就有网表。

开始导出网表。

出现红色划线部份说明导出成功了,否则会弹出1个对话框告知你有毛病的地方。

网表导出后多的1个文件夹。

2.建立PCB工程

建立PCB工程文件我相信誉过cadence的都会,操作没有变。

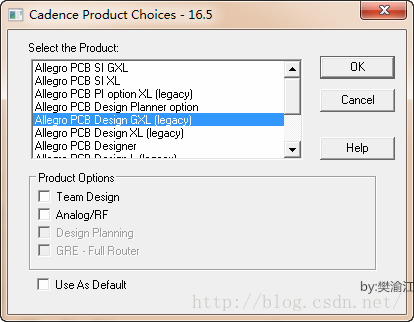

点开 PCB Editor 出现下面对话框,选择版本就OK了,GXL就是功能最多的。

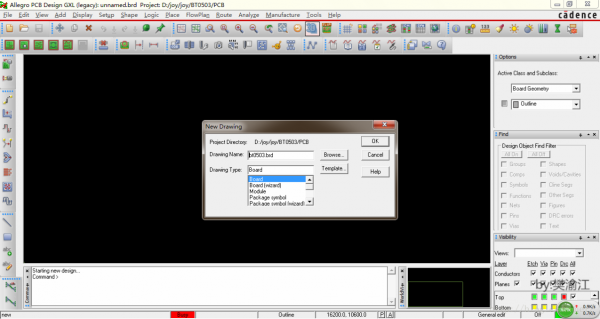

进入界面后点击File – New 就会出现下面对话框,选择board,添上工程名,选择存储路径,点击OK。就建好PCB工程了(扼要带过,会cadence的应当都非常清楚)。

3.界面参数设置

我们需要设置页面大小,还有栅格点,这样方便我们后续的工作

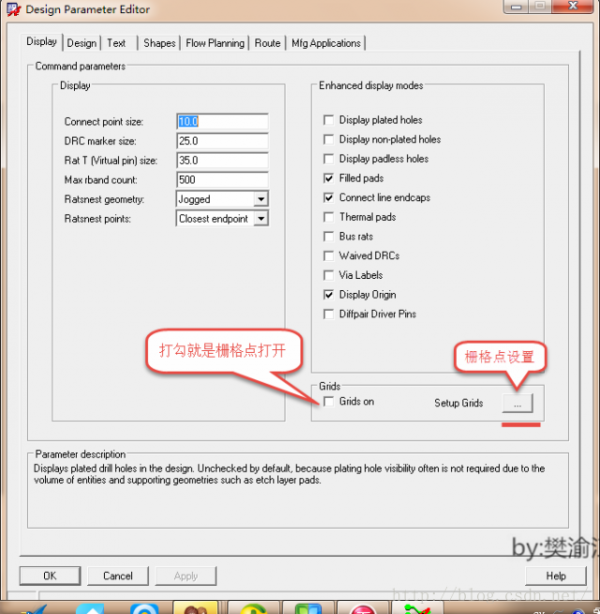

先是栅格,点击setup – Design Parameter Editor,出现下图

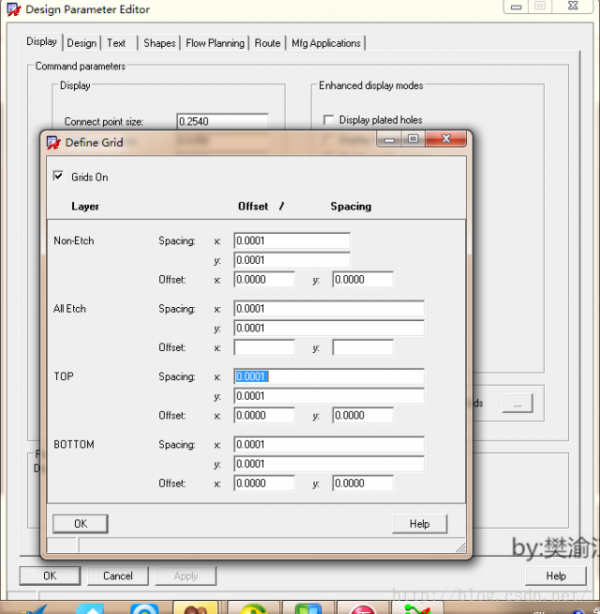

点击栅格点设置就会出现下图

里面有顶层、底层、电气层的栅格点最小间距设置,x和y分别代表x轴方向和y轴方向的栅格点,由于我的板子很小所以我设置的是最小。

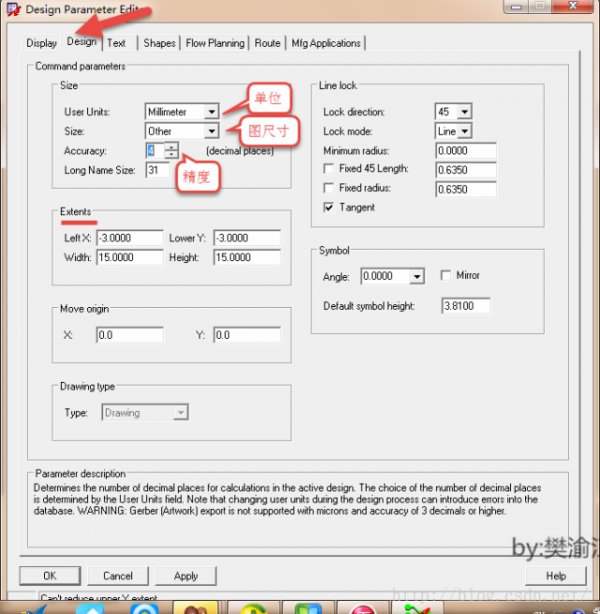

下1步是设置页面和全部工程使用的距离单位、距离精度。

Extents 里面是设置图纸大小(图纸尺寸栏选择了 other ,这就能够设置)和设置原点位置(网上有许多教程讲这个)。精度栏最大的就是4了。单位我们选择毫米。

4.导入网表

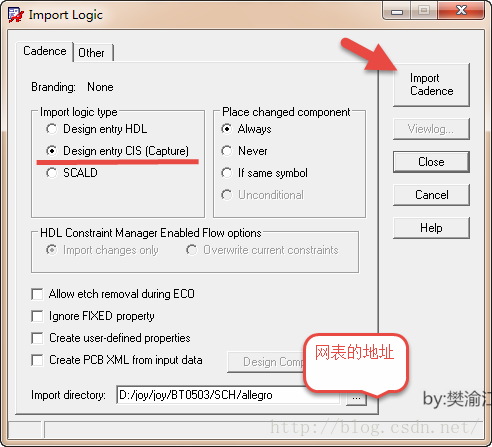

点击File – Import – Logic 就出现下图

第1次导入网表的时候要选择网表的路径,就是刚才导出原理图网表的路径,然后选择生成网表的工具,我们是用的Cadence自带的原理图工具(就是有划红线的选项),如果是其他软件做的网表就要选other。最后点击Import Cadence 网表就成功导入了。

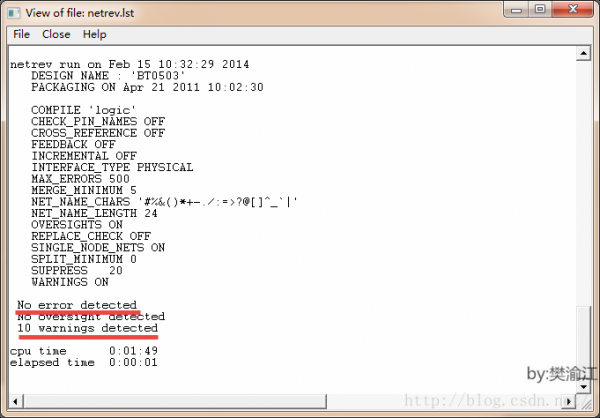

以上就是导入网表后的反馈信息,可以看见毛病和正告。

5.PCB板外框设计。

PCB外框需要画出物理外框、布线区域、器件放置区域,这几个是最重要的,有其他需要就添加其他的。

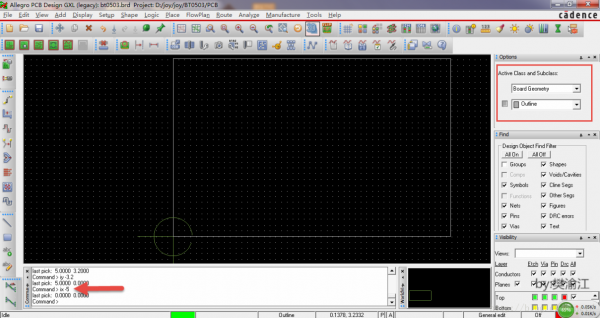

首先添加外框点击Add – Line 选择所属类(右侧红框内)。Line是走线的意思,可以手工画1个框也能够坐标画。我的图是用坐标画的,点击Line和选好类后在指令栏中输入 x 0 0(从原点起画,x和0、0和0之间有个空格)点回车,iy 3.2(向Y轴正向画3.2mm) 点回车,ix 5(向x轴正向画5mm)点回车, iy ⑶.2(向Y负向轴画3.2mm)点回车,ix ⑸(向x轴负向画5mm)点回车,1个方框就行了,也能够直接输4个顶点的坐标画全部方框。

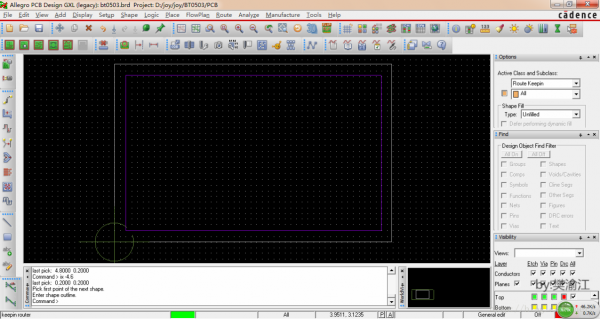

外框画好后就是开始画允许布线区域和允许期间放置区域

点击 setup – Areas – Package Keepin 和 Route Keepin画方框,方框的大小依照厂家的标准最好(1般都比外框小0.2mm)。

6.板层设置

点击Setup – Cross Setion

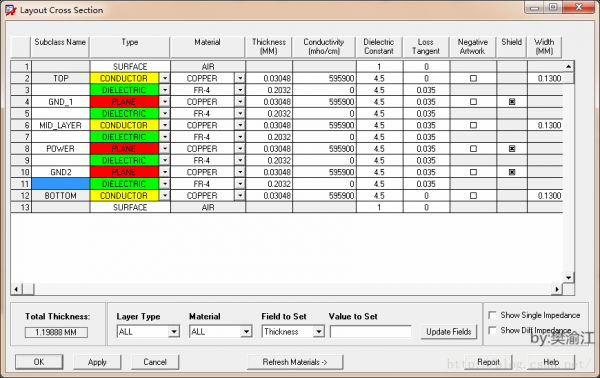

默许的时候只有顶层和底层,我们需要添加层,具体按自己的需求吧,我们这是6层。

就需要设置1下,在前面的序号上点击鼠标右键,会出现1个下拉框里面有两个选项 Add Layer Above(在当前层之上添加) 和 Add Layer Below(在当前层之下添加)。然后添加4层,每层之间需要1个介质层,默许选择就能够。现在设置每层的属性,在Type这1栏选择,中间的地层和电源层选择平面(plane),需要埋阻埋容层必须设成导电层。

下图就是我针对我的PCB设置的板层结构。

层设置好了就需要对埋阻埋容进行设置

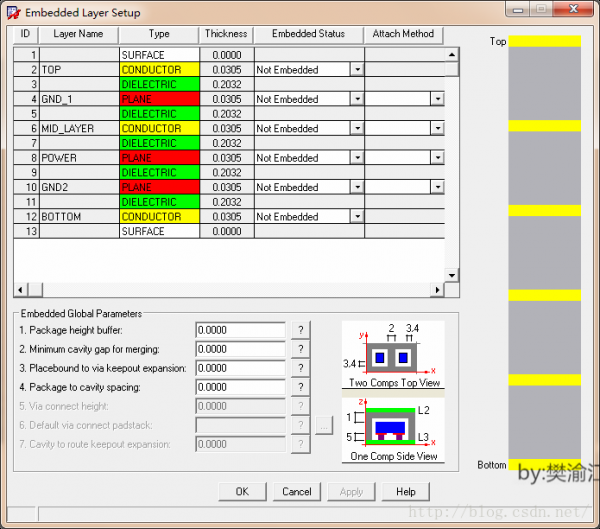

点击Setup – Embedded layer Setup出现下面对话框

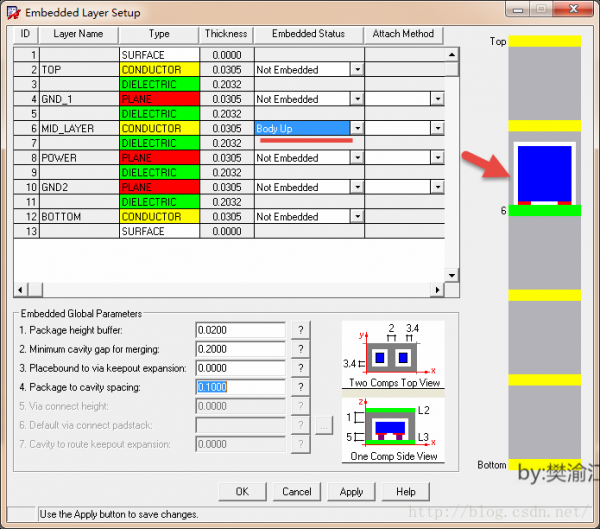

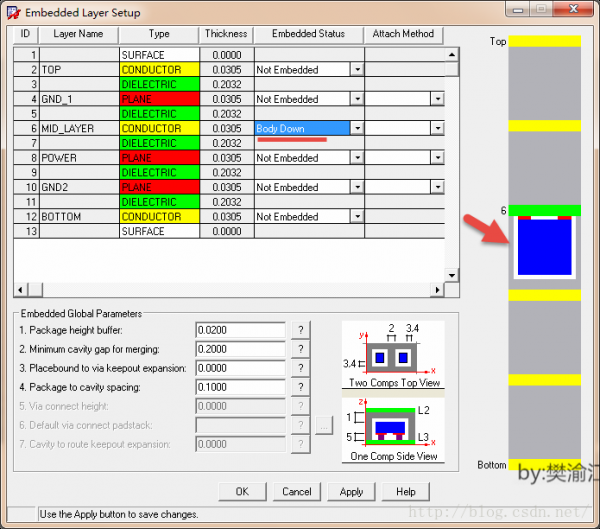

我们需要设置我们的第3层埋阻埋容,以下图

其中上半部份为叠层设置,Embedded Status设置埋入式器件状态,即设置内层器件方向:Body up表示器件在内导电层之上;Body down表示器件在内导电层之下;Not Embedded表示该叠层不允许放置埋入器件;Protruding Allowed表示允许器件突出,即允许该内层下方或上方的导电层凸出本层,以下图所示。Attach Method用以设置埋入式器件的连接方式,包括:Direct Attach表示埋入式器件直接连接内电层;Indirectly Attach表示埋入式器件非直接连接上内电层,即以焊盘连接到内电层向外连接。

下半部份Embedded Global Parameters全局埋入式器件的叠层设置参数,其意义在右侧的坐标中有对应显示,包括: Package height buffer:定义埋入式器件腔体与相邻叠层的距离限制; Minimum cavity gap for merging:定义腔体合成的最小距离,如25mil,即两个埋入式器件腔体间距接近至25mil以下时,两腔体即作甚1个腔体; Placebound to via keepout expansion:定义器件的封装Placebound到器件外部制止放置过孔区域的延伸距离; Package to cavity spacing:定义器件封装外部至埋入式腔体的间距; Via connect height:定义埋入式器件向外连接时,所用过孔的高度; Default via connect padstack:定义默许情况,允许和埋入式器件向外过孔相连接的焊盘类型; Cavity to route keepout expansion:定义埋入式器件腔体至该叠层制止布线区域之间的间距。

7.器件设置

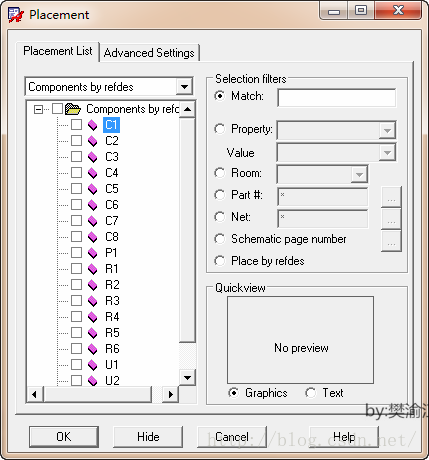

左侧是没有设置电阻电容可以埋入,右侧是设置了电阻电容可以埋入。

具体设置以下:

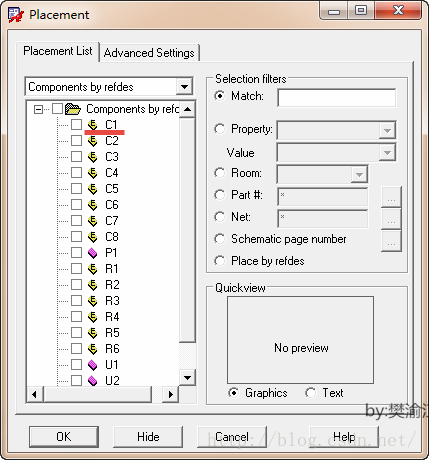

点击Setup – Constraints – Constraint Manager ,会出现以下对话框

在Embedded属性栏中,Placement列用以定义器件的埋入式属性,为某个器件定义Embedded/Placement属性,这些器件就能够在PCB中作为埋入式器件放入PCB内层,该属性包括:Option可选埋入式,则该器件可放在表面层,也能够作为埋入式器件放入内层;Required必要埋入式属性,则该器件必须作为埋入式器件放在内层,不可以置于表面层;External Only只外置属性,则该器件只能放在表面层,不可以作为埋入式器件置于内层。

8.放置器件

点击place – Manually 出现以下对话框,在器件前打勾就能够放置器件了(不要点OK)直接移动鼠标就能够看到器件随着鼠标走,点击鼠标右键有1个选项Place On Layer 里面有各个层的名字,点击就能够将器件放置到对应的层去,默许的是顶层。

如果放置器件的时候出现毛病,没有器件随着鼠标移动,那说明是你的库没有导进来。

点击 Setup – User Preferences 出现下图

把红线部份东西点击,导入你的pad和封装的库,就OK了。

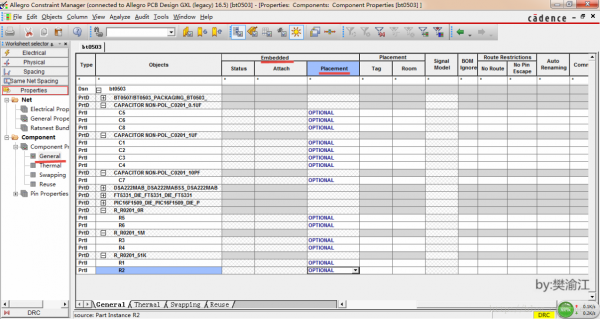

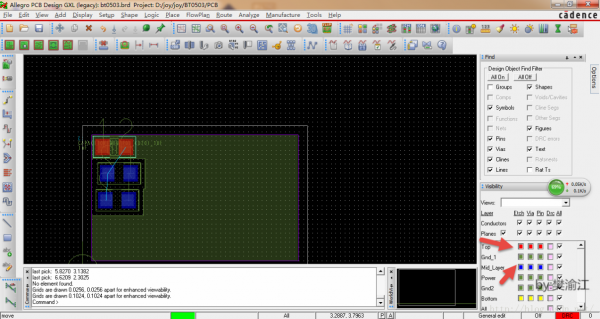

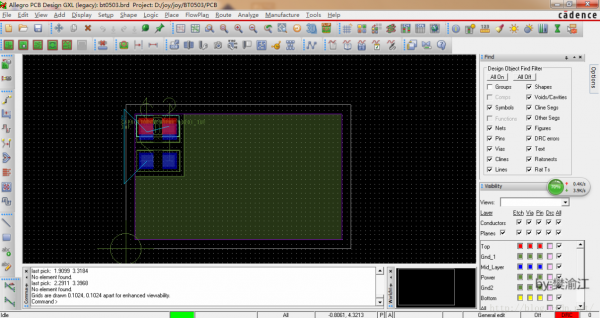

以下是放置好后的器件

红色是顶层,蓝色是中间层了。

大功告成,顶层和中间层都放有器件。

如果两个期间像上图那样有堆叠的时候,需要修改1下DRC,由于他默许2维空间里这两个器件堆叠了,但是在3维空间里他们是没有堆叠的。

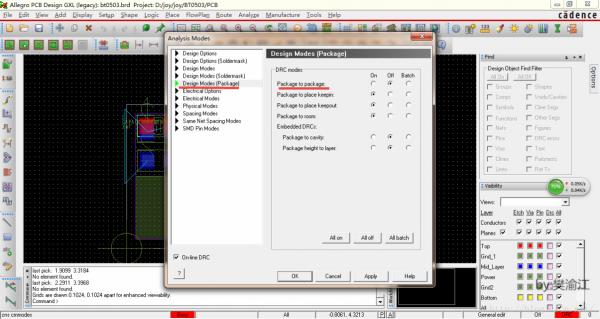

点击Setup – Constraints –Modes 出现下图

把红线部份选成off就行了。

全部埋阻埋容的设计就OK了,剩下的就是布局布线了。这个我相信大家都能弄清楚的。